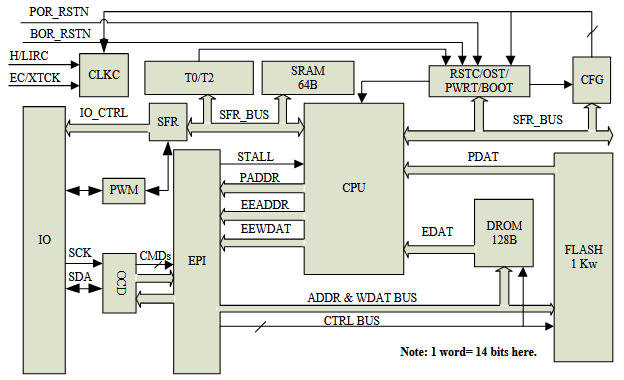

在當今電子設備設計中,工程師常常面臨一個挑戰:如何在有限的空間和成本內實現功能的多樣化和高效性。FT60F210-URT 正是為解決這一問題而生。它以極小的封裝(SOT23-6)和高度集成的設計,提供了從存儲到外設的全面功能,適用于各種對空間和成本敏感的應用場景。本文將深入解析 FT60F210-URT 的系統框圖、管腳定義以及其核心特性,幫助工程師快速掌握其設計要點,提升開發效率。

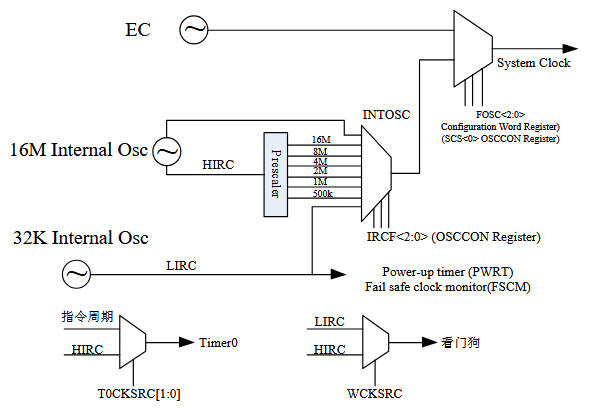

關鍵信號鏈:

HIRC/LIRC → 時鐘選擇器 → CPU/Timer/PWM → GPIO → 外部世界

Touch 模塊共享 GPIO,內部 10 nF 基準電容,無需外接。

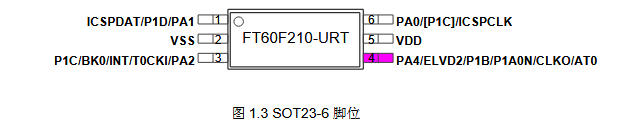

| 管腳 | 名 | 主功能 | 第二/復用 | 說明 |

|---|---|---|---|---|

| 1 | VDD | 2.0-5.5 V 供電 | — | 內置 LVR 2.0/2.2/2.5…4.1 V 可選 |

| 6 | VSS | 地 | — | 星點接地 |

| 2 | PA0 | 數字 IO | ICSPCLK/TK0/P1C | 燒錄時鐘+觸摸通道+PWM |

| 3 | PA1 | 數字 IO | ICSPDAT/TK1/P1D | 燒錄數據+觸摸+PWM |

| 5 | PA2 | 數字 IO | INT/T0CKI/TK2/P1C | 外部中斷/計數器輸入/觸摸 |

| 4 | PA4 | 數字 IO | CLKO/ELVD1/P1B/P1A0N | 時鐘輸出/外部LVD/PWM |

設計提示:

| 項目 | 容量 | 備注 |

|---|---|---|

| Flash | 1K ×14 | 0x000-0x3FF,最后 16 字為中斷向量 |

| SRAM | 64 B | 0x20-0x5F,Bank0 |

| EEPROM | 128 B | 獨立地址空間,2 ms 自定時寫完成 |

| 堆棧 | 8 級硬件 | 不可軟件訪問,子程序/中斷自動壓棧 |

| 外設 | 說明 |

|---|---|

| Timer0 | 8 位,共用 8 位預分頻,可外部計數 |

| Timer2 | 16 位,PR2 雙緩沖,后分頻 1-16 |

| PWM1 | 4 路獨立 16 位占空比,P1A 帶互補死區,最高 256 kHz(16M/64/1024) |

| Touch | 4 通道,自動掃描,閾值可設,中斷喚醒 |

| WDT | 16 位,LIRC/HIRC 可選,1-65536 分頻 |

| LVD | 1.2-4.0 V 8 檔,可測外部電壓,作剎車源 |

VDD ──?104──┐

C

│

PA4──LED_R──┤

PA0──LED_G──┤ 共陽 RGB

PA1──LED_B──┘

PA2──按鍵(觸摸或機械)

VSS─────────?GND

FT60F210-URT 把“最小系統”濃縮成一顆 SOT23-6:

FT60F210-URT 以其極小的封裝和強大的功能集成,為工程師提供了一種高效、靈活的解決方案。它不僅滿足了現代電子設備對低功耗、高集成度和快速開發的需求,還通過減少外圍元件數量,顯著降低了系統成本和設計復雜性。深圳三佛科技提供樣品,技術支持~